Цифровое оборудование | ||||||||||||||||||||||||||||||||||||||||||

| Главная > Как устроен процессор > Синхронизация узлов процессора > | ||||||||||||||||||||||||||||||||||||||||||

| Меню: |

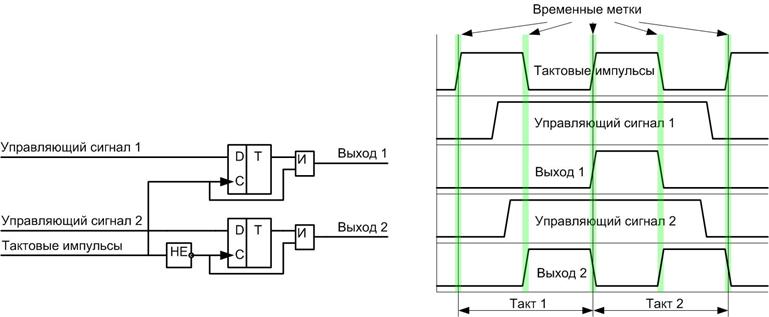

Синхронизация узлов процессораПривязка управляющих сигналов. Соответственно, для узлов комбинационного типа в качестве управляющих сигналов можно напрямую использовать данные, извлекаемые из памяти микрокоманд. Сигналы для узлов с памятью должны изменять свое значение строго в момент очередной временной метки в зависимости от соответствующего управляющего сигнала. Для привязки этих управляющих сигналов к временным меткам можно применить такую схему:

Эта схема состоит из двух частей. Верхняя часть схемы привязывает управляющий сигнал 1 к концу тактового импульса, нижняя – к середине. Если фиксация данных в каком-либо узле с памятью осуществляется при изменении управляющего сигнала из нуля в единицу, то узлы, управляемые первым сигналом будут фиксировать данные в конце периода тактового импульса, вторым – в середине. Большинство узлов с памятью, входящих в состав процессора должны фиксировать данные в конце периода тактового сигнала и соответственно управляться сигналом первого типа. Входные регистры АЛУ должны фиксировать данные в середине периода тактового импульса, если в них записываются полученные из регистрового файла аргументы команды, и в конце периода, если в них фиксируется результат операции. Следовательно, для управления каждым регистром необходимо не один, а два управляющих сигнала – один для фиксации аргументов, и другой – для фиксации результата. Теперь можно сформулировать более точно список необходимых управляющих сигналов процессора и их привязку к тактовым импульсам. Если сократить совпадающие сигналы в полученном ранее списке, останется 24 управляющих сигнала. Часть из них не требует временной привязки к тактовым импульсам, часть должна оказывать действие в середине периода, и часть – в конце. Тогда получится следующая таблица:

С описанным трактом данных и таким форматом микрокоманды можно организовать выполнение ограниченного набора элементарных команд и считывание команд из оперативной памяти. В этом случае, каждая команда будет состоять из одной микрокоманды, и выполняться за один такт. Такие процессоры реально существуют и составляют отдельный класс RISC процессоров (процессоры с сокращенным набором команд). В таких процессорах в качестве аргументов команд можно использовать только регистры, а для обращений к оперативной памяти необходимы специальные команды загрузки данных из оперативной памяти в регистры. Выбор самих команд в таких процессорах весьма ограничен. Но не смотря на такие ограничения, процессоры этого класса позволяют решать весьма широкий круг задач. Однако для выполнения более сложных, чем простое сложение, арифметических операции, для выполнения команд над аргументами, хранящимися в оперативной памяти, выполнение одной команды может потребовать нескольких микрокоманд. Следовательно, каким-то образом необходимо организовать их последовательное исполнение. А для этого может пригодиться рассмотренная ранее управляющая схема из трех элементов – памяти микрокоманд, регистра адреса микрокоманды и селектора условий. Она-то и послужит тем механизмом, который будет выполнять последовательность микрокоманд для каждой выполняемой команды. Автор текста - Молчанов Н.Н. |

Дополнительно: | ||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||