Цифровое оборудование | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Главная > Как устроен процессор > Сдвиговые регистры, сумматоры > | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Меню: |

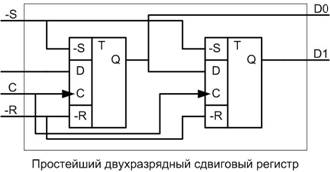

Сдвиговые регистры, сумматорыСдвиговые регистры. Если соединять входы и выходы данных триггеров последовательно, так чтобы выход предыдущего соединялся со входом последующего триггера, можно получить сдвиговый регистр. Разряд данных, записанный первым управляющим импульсом в первый триггер, с каждым последующим импульсом будет сдвигаться в следующий триггер.

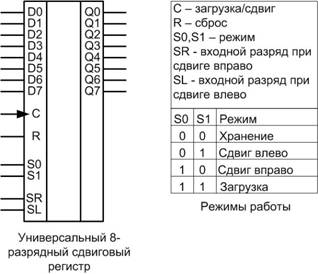

Существует множество разновидностей счетчиков и сдвиговых регистров, предназначенных для различных применений. Например, в различных приборах широко используют счетчики, имеющие диапазон счета от 0 до 10, в электронных часах – счетчики от 0 до 12. Сдвиговые регистры применяют для преобразования параллельного кода в последовательный, и обратно.

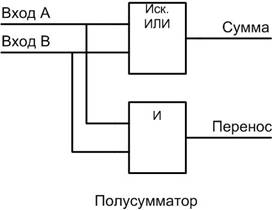

Сумматор Еще одним важным узлом является сумматор. Смысл его в том, чтобы получить арифметическую сумму входных сигналов в двоичном коде. Если мы сложим два одноразрядных двоичных числа, то у нас получится: 0+0=0, 1+0=1, 0+1=1, 1+1=10. Если в первых трех случаях сумма двух одноразрядных двоичных чисел осталась одноразрядной, то в последнем случае она стала двухразрядной. Если мы будем складывать двухразрядные двоичные числа, то получившийся лишний разряд в младшем разряде, нам нужно будет добавить к сумме старших разрядов. Таким образом, при сложении может возникать перенос, который нужно учитывать в следующем разряде. И соответственно, одноразрядный сумматор должен иметь не один, а два выхода. Простейший сумматор можно получить, если соединить элемент «Исключающее ИЛИ» с элементом «И» как показано на рисунке.

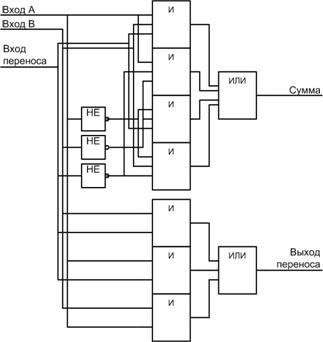

И действительно, младший разряд суммы должен быть единицей, если единица присутствует только в одном из слагаемых разрядов, что в точности соответствует элементу «Исключающее ИЛИ», а перенос должен быть единицей, только если единица присутствует в обоих складываемых разрядах. Однако, если при помощи двух таких сумматоров мы захотим сложить два двухразрядных числа, то у нас ничего не получится – сумматор в старшем разряде не сможет учитывать перенос из младшего разряда. Поэтому такая схема называется полусумматором. Полный сумматор Полный сумматор должен учитывать входной перенос, и его схема существенно сложнее.

Так выглядит схема полного сумматора и таблица, поясняющая его работу. Такие сумматоры можно объединять для сложения многоразрядных двоичных чисел. При таком объединении вход переноса каждого разряда должен быть соединен с выходом переноса предыдущего разряда. Таким образом, перенос распространяется последовательно от младшего разряда к старшему. Каждый разряд, через который распространяется перенос, вносит некоторую временную задержку в его распространение, и чем больше разрядность суммируемых чисел, тем больше времени требуется на распространение переноса. Поэтому существуют специальные логические схемы, позволяющие ускорять этот процесс. Автор текста - Молчанов Н.Н. |

Дополнительно: | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||